(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-213120

(P2019-213120A)

(43) 公開日 令和1年12月12日(2019.12.12)

| (51) Int.Cl. |              | F 1              |      | テーマコード (参考) |            |

|--------------|--------------|------------------|------|-------------|------------|

| <b>H04N</b>  | <b>7/18</b>  | <b>(2006.01)</b> | H04N | 7/18        | M 2 H04 O  |

| <b>A61B</b>  | <b>1/045</b> | <b>(2006.01)</b> | A61B | 1/045       | 610 4 C161 |

| <b>H04N</b>  | <b>5/225</b> | <b>(2006.01)</b> | H04N | 5/225       | 500 5 C054 |

| <b>H04N</b>  | <b>5/232</b> | <b>(2006.01)</b> | H04N | 5/232       | 300 5 C122 |

| <b>G02B</b>  | <b>23/24</b> | <b>(2006.01)</b> | G02B | 23/24       | B          |

審査請求 未請求 請求項の数 14 O L (全 20 頁) 最終頁に続く

|           |                              |            |                                                                                                                                                           |

|-----------|------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2018-109615 (P2018-109615) | (71) 出願人   | 000000376<br>オリンパス株式会社<br>東京都八王子市石川町2951番地                                                                                                                |

| (22) 出願日  | 平成30年6月7日(2018.6.7)          | (74) 代理人   | 110002147<br>特許業務法人酒井国際特許事務所                                                                                                                              |

|           |                              | (72) 発明者   | 大澤 雅人<br>東京都八王子市石川町2951番地 オリ<br>ンパス株式会社内                                                                                                                  |

|           |                              | F ターム (参考) | 2H040 DA22 GA02 GA06 GA11<br>4C161 CC06 NN01 NN03 SS07 SS12<br>UU02 UU09<br>5C054 CA04 CC02 ED12 HA12<br>5C122 DA26 EA54 GC52 GC86 HA34<br>HB02 HB07 HB10 |

(54) 【発明の名称】 映像取得装置および内視鏡

## (57) 【要約】

【課題】さらなる伝送ケーブルの細径化と高速な信号伝送との両立を図ることができる映像取得装置および内視鏡を提供する。

【解決手段】映像取得装置は、第1のバッファ26と、第1のバッファ26から入力された第2の映像信号の内、所定の周波数よりも高い周波数成分のみを透過しつつ増幅を行った第3の映像信号を出力するプリエンファシスアンプ27と、プリエンファシスアンプ27から入力された第3の映像信号に対して増幅を行った第4の映像信号を伝送ケーブル3の入力端子へ出力する第2のバッファ28と、プリエンファシスアンプ27の出力端子における直流インピーダンスは、第1のインピーダンス素子53の直流インピーダンスよりも高い。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

映像信号を送信する送信部と、

第1の特性インピーダンスを有し、前記映像信号を伝送する伝送ケーブルと、

前記伝送ケーブルを伝送された前記映像信号を受信する受信部と、

を備え、

前記送信部は、

外部から入力された第1の映像信号に対して増幅を行ったローインピーダンスの第2の映像信号として出力する第1のバッファと、

前記第1のバッファから入力された前記第2の映像信号の内、所定の周波数よりも高い周波数成分のみを透過しつつ増幅を行った第3の映像信号を出力するプリエンファシスアンプと、

前記プリエンファシスアンプから入力された前記第3の映像信号に対して増幅を行った第4の映像信号を前記伝送ケーブルの入力端子へ出力する第2のバッファと、

を有し、

前記受信部は、

前記伝送ケーブルの基端側に接続され、前記伝送ケーブルにおける前記第1の特性インピーダンスとの整合を行う第1のインピーダンス素子と、

を有し、

前記プリエンファシスアンプの出力端子における直流インピーダンスは、前記第1のインピーダンス素子の直流インピーダンスよりも高い映像取得装置。

**【請求項 2】**

前記送信部は、

一端側が前記伝送ケーブルの先端側に接続され、他端側が前記第2のバッファの出力端に接続され、前記伝送ケーブルにおける前記第1の特性インピーダンスとの整合を行う第2のインピーダンス素子を有する

請求項1に記載の映像取得装置。

**【請求項 3】**

前記プリエンファシスアンプは、

一端側が前記第1のバッファの出力端子に接続され、他端側が前記第2のバッファの入力端子に接続される

請求項1または2に記載の映像取得装置。

**【請求項 4】**

前記プリエンファシスアンプは、ハイパスフィルタである

請求項1～3のいずれか一つに記載の映像取得装置。

**【請求項 5】**

前記送信部は、

所定の値を有する基準レベル信号と前記第4の映像信号とを交互に前記伝送ケーブルへ出力し、

前記受信部は、

前記基準レベル信号の値と前記第4の映像信号の値の差分をデジタル信号に変換するA/D変換部を有する

請求項1～4のいずれか一つに記載の映像取得装置。

**【請求項 6】**

前記第2のバッファは、フィードフォード型のアンプである

請求項1～5のいずれか一つに記載の映像取得装置。

**【請求項 7】**

前記第2のバッファは、

第1導電型のトランジスタを有し、

10

20

30

40

50

前記第1導電型のトランジスタは、ゲート端子に前記第3の映像信号が入力され、ドレン端子が電源電圧に接続され、ソース端子が前記伝送ケーブルに接続される

請求項1～6のいずれか一つに記載の映像取得装置。

【請求項8】

前記送信部は、

前記プリエンファシスアンプに接続され、前記第1導電型のトランジスタの閾値ばらつきをキャンセルする電圧を供給するバイアス回路をさらに有する

請求項7に記載の映像取得装置。

【請求項9】

前記送信部は、

前記バイアス回路へ電流を供給する定電流源をさらに有する

請求項8に記載の映像取得装置。

10

【請求項10】

前記プリエンファシスアンプは、カットオフ周波数が前記伝送ケーブルのカットオフ周波数以上である

請求項1～6のいずれか一つに記載の映像取得装置。

【請求項11】

前記プリエンファシスアンプは、

フィードバックネットワークを有するフィードバックアンプと、

前記フィードバックネットワーク内に設けられ、前記フィードバックアンプの周波数依存性を有するインピーダンス素子群と、

20

を含む

請求項1～6のいずれか一つに記載の映像取得装置。

【請求項12】

前記送信部は、

光を受光することによって前記第1の映像信号を生成する撮像素子をさらに有する

請求項1～11のいずれか一つに記載の映像取得装置。

20

【請求項13】

前記送信部は、

前記撮像素子および前記第1のバッファが配置されてなる第1チップと、

30

前記プリエンファシスアンプおよび前記第2のバッファが配置されてなる第2チップと

、

をさらに有し、

前記第1チップは、前記第2チップに積層されてなる

請求項12に記載の映像取得装置。

【請求項14】

請求項1～13のいずれか一つに記載の映像取得装置と、

被検体に挿入可能な挿入部と、

前記映像信号に対して画像処理を行う制御装置に接続されるコネクタ部と、

40

を備え、

前記送信部は、前記挿入部の先端部に配置されてなり、

前記受信部は、前記コネクタ部に配置されてなる

内視鏡。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、伝送ケーブルを用いて映像信号を送信側から受信側へ送信する映像取得装置および内視鏡に関する。

【背景技術】

【0002】

50

従来、内視鏡システムでは、伝送ケーブルを用いて被検体の挿入部の先端部に設けられた撮像装置によって生成されたパルス状の映像信号をプロセッサへの伝送を行っている（特許文献1参照）。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特許第5596888号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、内視鏡システムにおいては、患者負担の軽減のため、伝送ケーブルのさらなる細径化が望まれている。しかしながら、伝送ケーブルの細径化を図った場合、細いケーブルほどパルス状の映像信号の波形がなまってしまい、高速な信号伝送を行うことができないという問題点があった。

【0005】

本開示は、上記に鑑みてなされたものであって、さらなる伝送ケーブルの細径化と高速な信号伝送との両立を図ることができる映像取得装置および内視鏡を提供することを目的とする。

【課題を解決するための手段】

【0006】

上述した課題を解決し、目的を達成するために、本開示に係る映像取得装置は、映像信号を送信する送信部と、第1の特性インピーダンスを有し、前記映像信号を伝送する伝送ケーブルと、前記伝送ケーブルを伝送された前記映像信号を受信する受信部と、を備え、前記送信部は、外部から入力された第1の映像信号に対して増幅を行ったローインピーダンスの第2の映像信号として出力する第1のバッファと、前記第1のバッファから入力された前記第2の映像信号の内、所定の周波数よりも高い周波数成分のみを透過しつつ増幅を行った第3の映像信号を出力するプリエンファシスアンプと、前記プリエンファシスアンプから入力された前記第3の映像信号に対して増幅を行った第4の映像信号を前記伝送ケーブルの入力端子へ出力する第2のバッファと、を有し、前記受信部は、前記伝送ケーブルの基端側に接続され、前記伝送ケーブルにおける前記第1の特性インピーダンスとの整合を行うインピーダンス素子と、を有し、前記プリエンファシスアンプの出力端子における直流インピーダンスは、前記第1のインピーダンス素子の直流インピーダンスよりも高い。

【0007】

また、本開示に係る映像取得装置は、上記開示において、前記送信部は、一端側が前記伝送ケーブルの先端側に接続され、他端側が前記第2のバッファの出力端に接続され、前記伝送ケーブルにおける前記第1の特性インピーダンスとの整合を行う第2のインピーダンス素子を有する。

【0008】

また、本開示に係る映像取得装置は、上記開示において、前記プリエンファシスアンプは、一端側が前記第1のバッファの出力端子に接続され、他端側が前記第2のバッファの入力端子に接続される。

【0009】

また、本開示に係る映像取得装置は、上記開示において、前記プリエンファシスアンプは、ハイパスフィルタである。

【0010】

また、本開示に係る映像取得装置は、上記開示において、前記送信部は、所定の値を有する基準レベル信号と前記第4の映像信号とを交互に前記伝送ケーブルへ出力し、前記受信部は、前記基準レベル信号の値と前記第4の映像信号の値の差分をデジタル信号に変換するA/D変換部を有する。

10

20

30

40

50

**【0011】**

また、本開示に係る映像取得装置は、上記開示において、前記第2のバッファは、フィードフォード型のアンプである。

**【0012】**

また、本開示に係る映像取得装置は、上記開示において、前記第2のバッファは、第1導電型のトランジスタを有し、前記第1導電型のトランジスタは、ゲート端子に前記第3の映像信号が入力され、ドレイン端子が電源電圧に接続され、ソース端子が前記伝送ケーブルに接続される。

**【0013】**

また、本開示に係る映像取得装置は、上記開示において、前記送信部は、前記プリエンファシスアンプに接続され、前記第1導電型のトランジスタの閾値ばらつきをキャンセルする電圧を供給するバイアス回路をさらに有する。

**【0014】**

また、本開示に係る映像取得装置は、上記開示において、前記送信部は、前記バイアス回路へ電流を供給する定電流源をさらに有する。

**【0015】**

また、本開示に係る映像取得装置は、上記開示において、前記プリエンファシスアンプは、カットオフ周波数が前記伝送ケーブルのカットオフ周波数以上である。

**【0016】**

また、本開示に係る映像取得装置は、上記開示において、前記プリエンファシスアンプは、フィードバックネットワークを有するフィードバックアンプと、前記フィードバックネットワーク内に設けられ、前記フィードバックアンプの周波数依存性を有するインピーダンス素子群と、を含む。

**【0017】**

また、本開示に係る映像取得装置は、上記開示において、前記送信部は、光を受光することによって前記第1の映像信号を生成する撮像素子をさらに有する。

**【0018】**

また、本開示に係る映像取得装置は、上記開示において、前記送信部は、前記撮像素子および前記第1のバッファが配置されてなる第1チップと、前記プリエンファシスアンプおよび前記第2のバッファが配置されてなる第2チップと、をさらに有し、前記第1チップは、前記第2チップに積層されてなる。

**【0019】**

また、本開示に係る内視鏡は、上記開示の映像取得装置と、被検体に挿入可能な挿入部と、前記映像信号に対して画像処理を行う制御装置に接続されるコネクタ部と、を備え、前記送信部は、前記挿入部の先端部に配置されてなり、前記受信部は、前記コネクタ部に配置されてなる。

**【発明の効果】****【0020】**

本開示によれば、さらなる伝送ケーブルの細径化と高速な信号伝送との両立を図ることができるという効果を奏する。

**【図面の簡単な説明】****【0021】**

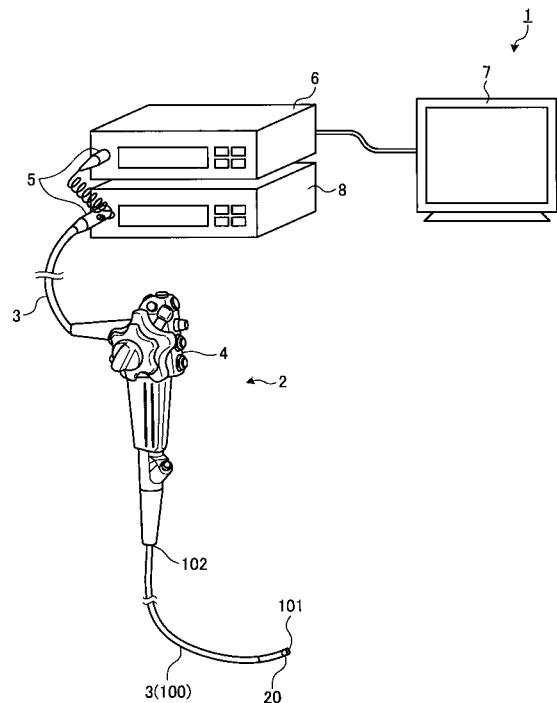

【図1】図1は、本開示の実施の形態1に係る内視鏡システムの全体構成を模式的に示す概略図である。

【図2】図2は、本開示の実施の形態1に係る内視鏡システムの要部の機能構成を示すブロック図である。

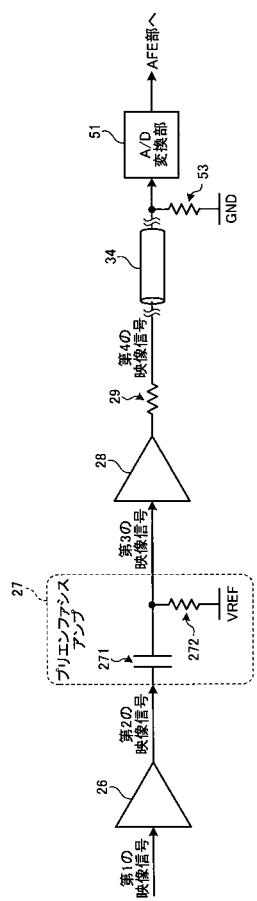

【図3】図3は、本開示の実施の形態1に係るプリエンファシスアンプの構成を示す回路図である。

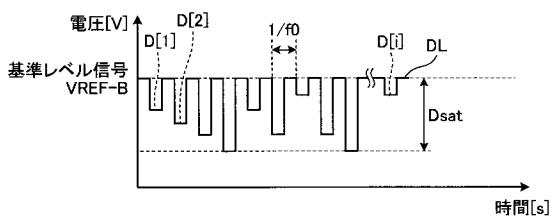

【図4】図4は、本開示の実施の形態1に係る撮像部が送信する第4の映像信号を表すタイミングチャートである。

10

20

30

40

50

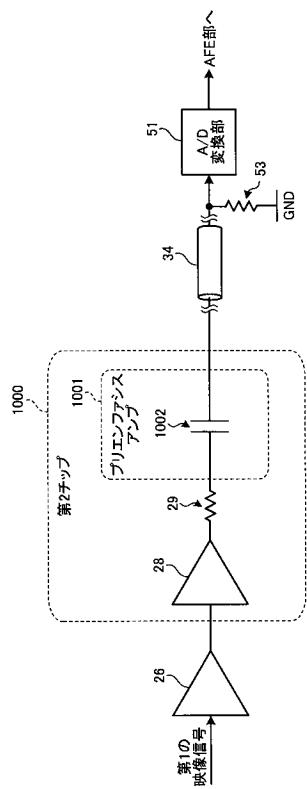

【図5】図5は、比較例のプリエンファシスアンプを備える回路図を模式的に示す図である。

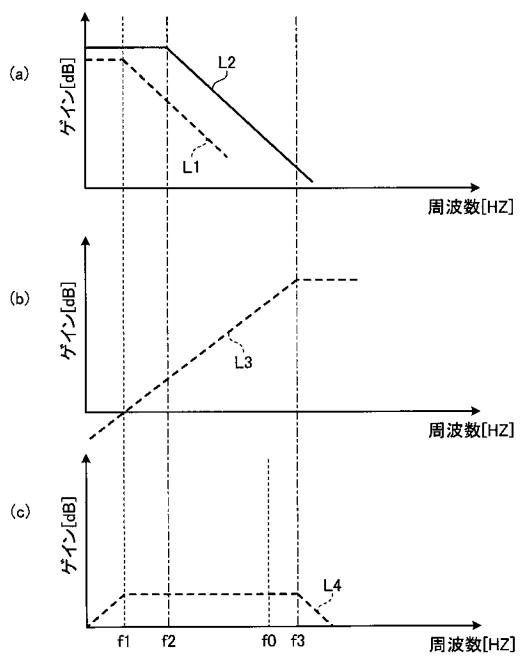

【図6】図6は、本開示の実施の形態1に係るプリエンファシスアンプの効果を模式的に示す図である。

【図7】図7は、本開示の実施の形態1に係る撮像部が送信する映像信号の時間変化を示す図である。

【図8】図8は、本開示の実施の形態2に係る撮像装置の要部を含む回路図である。

【図9】図9は、本開示の実施の形態2の変形例に係る撮像装置の要部を含む回路図である。

【図10】図10は、本開示の実施の形態3に係る撮像装置の要部を含む回路図である。

10

【発明を実施するための形態】

【0022】

以下、本開示を実施するための形態（以下、「実施の形態」という）として、被検体内に挿入される挿入部の先端部に撮像装置を有する内視鏡を備えた内視鏡システムについて説明する。また、この実施の形態により、本開示が限定されるものではない。さらに、図面の記載において、同一の部分には同一の符号を付して説明する。さらにまた、図面は、模式的なものであり、各部材の厚みと幅との関係、各部材の比率等は、現実と異なることに留意する必要がある。また、図面の相互間において、互いの寸法や比率が異なる部分が含まれている。

【0023】

（実施の形態1）

〔内視鏡システムの構成〕

図1は、本開示の実施の形態1に係る内視鏡システムの全体構成を模式的に示す概略図である。図1に示す内視鏡システム1は、内視鏡2と、伝送ケーブル3と、コネクタ部5と、プロセッサ6と、表示装置7と、光源装置8と、を備える。

【0024】

内視鏡2は、伝送ケーブル3の一部である挿入部100を被検体の体腔内に挿入することによって被検体の体内を撮像して撮像信号をプロセッサ6へ出力する。また、内視鏡2は、伝送ケーブル3の一端側であり、被検体の体腔内に挿入される挿入部100の先端部101側に、被検体の体内を撮像して映像信号を生成する撮像装置20が設けられている。さらに、内視鏡2は、挿入部100の基端部102側に、内視鏡2に対する各種操作を受け付ける操作部4が設けられている。撮像装置20が撮像した体内画像の映像信号は、例えば数mの長さを有する伝送ケーブル3を経由してコネクタ部5に出力される。なお、実施の形態1では、撮像装置20が映像取得装置の送信部として機能する。

【0025】

伝送ケーブル3は、内視鏡2とコネクタ部5とを接続するとともに、内視鏡2とプロセッサ6および光源装置8とを接続する。また、伝送ケーブル3は、撮像装置20が生成した撮像信号をコネクタ部5へ伝送する。伝送ケーブル3は、ケーブルや光ファイバ等を用いて構成される。また、伝送ケーブル3は、第1のインダクタンスを有する。具体的には、伝送ケーブル3は、例えば50の特性インピーダンスを有する。

【0026】

コネクタ部5は、内視鏡2、プロセッサ6および光源装置8に接続され、接続された内視鏡2が出力する映像信号に所定の信号処理を施してプロセッサ6へ出力する。なお、実施の形態1では、コネクタ部5が映像取得装置の受信部として機能する。

【0027】

プロセッサ6は、コネクタ部5から入力された映像信号に所定の画像処理を施して表示装置7へ出力する。また、プロセッサ6は、内視鏡システム1全体を統括的に制御する。例えば、プロセッサ6は、光源装置8が出射する照明光を切り替えたり、内視鏡2の撮像モードを切り替えたりする制御を行う。

【0028】

10

20

30

40

50

表示装置 7 は、プロセッサ 6 が画像処理を施した映像信号に対応する画像を表示する。また、表示装置 7 は、内視鏡システム 1 に関する各種情報を表示する。表示装置 7 は、液晶や有機 E L (Electro Luminescence) 等の表示パネル等を用いて構成される。

【 0 0 2 9 】

光源装置 8 は、コネクタ部 5 および伝送ケーブル 3 を経由して内視鏡 2 の挿入部 100 の先端部 101 側から被検体(被写体)に向けて照明光を照射する。光源装置 8 は、白色光を発する白色 L E D (Light Emitting Diode) 等を用いて構成される。なお、本実施の形態では、光源装置 8 に同時方式の照明方式が採用されるが、面順次方式の照明方式であってもよい。

〔内視鏡システムの要部〕

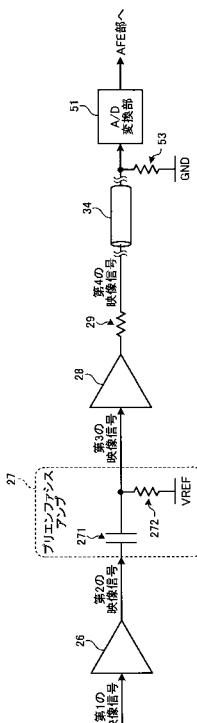

次に、内視鏡システム 1 の要部の機能について説明する。図 2 は、内視鏡システム 1 の要部の機能構成を示すブロック図である。

【 0 0 3 0 】

〔内視鏡の構成〕

まず、内視鏡 2 の構成について説明する。

図 2 に示す内視鏡 2 は、撮像装置 20 と、伝送ケーブル 3 と、コネクタ部 5 と、を備える。

【 0 0 3 1 】

撮像装置 20 は、第 1 チップ 21 と、第 2 チップ 22 と、を有する。第 1 チップ 21 および第 2 チップ 22 は、相対して貼り合わされ、チップ間は、チップの周縁部に配置されるパッド、またはチップ間を貫通するビア等により接続される。なお、第 1 チップ 21 および第 2 チップ 22 は、双方の正面が平行になるように配置するものに限らず、周囲の構造により、横に並べて配置したり、一方の正面に対して他方の正面が垂直になるように積層して配置したりしてもよい。

【 0 0 3 2 】

第 1 チップ 21 は、受光部 23 と、読み出し部 24 と、第 1 のバッファ 26 と、タイミング生成部 25 と、を有する。

【 0 0 3 3 】

受光部 23 は、図示しない光学系が集光した被写体像を受光することによって光電変換を行い、この光電変換によって第 1 の映像信号(画像信号)を生成する。受光部 23 は、受光量に応じた第 1 の映像信号を生成する複数の画像が行列方向に二次元マトリクス状に配置されてなる。受光部 23 は、C C D (Charge Coupled Device) や C M O S (Complementary Metal Oxide Semiconductor) 等のイメージセンサを用いて構成される。

【 0 0 3 4 】

読み出し部 24 は、タイミング生成部 25 の制御のもと、受光部 23 によって光電変換によって生成された第 1 の映像信号を列毎に順次読み出すことによって第 1 のバッファ 26 へ出力する。読み出し部 24 は、水平走査回路および垂直走査回路等を用いて構成される。

【 0 0 3 5 】

タイミング生成部 25 は、伝送ケーブル 3 から入力された基準クロック信号および同期信号に基づいて、読み出し部 24 を駆動するための駆動信号を生成し、この駆動信号を読み出し部 24 へ出力する。タイミング生成部 25 は、タイミングジェネレータ等を用いて構成される。

【 0 0 3 6 】

第 1 のバッファ 26 は、読み出し部 24 から入力された第 1 の映像信号を低インピーダンス(Low Impedance) の第 2 の映像信号として第 2 チップ 22 へ出力する。第 1 のバッファ 26 は、増幅アンプ、例えばフィードフォード型のアンプ等を用いて構成される。

【 0 0 3 7 】

第 2 チップ 22 は、プリエンファシスアンプ 27 と、第 2 のバッファ 28 と、第 1 のインピーダンス素子 29 と、を有する。

10

20

30

40

50

## 【0038】

プリエンファシスアンプ27は、一端側が第1のバッファ26の出力端子に接続され、他端側が第2のバッファの入力端子に接続される。プリエンファシスアンプ27は、第1のバッファ26から入力された第2の映像信号の内、所定の周波数よりも高い周波数成分のみを透過しつつ増幅を行った第3の映像信号を第2のバッファ28へ出力する。なお、プリエンファシスアンプ27の詳細な構成は、後述する。

## 【0039】

第2のバッファ28は、プリエンファシスアンプ27から入力された第3の映像信号の増幅を行った第4の映像信号を伝送ケーブル3（信号線34）へ出力する。第2のバッファ28は、出力アンプ等を用いて構成される。

10

## 【0040】

第1のインピーダンス素子29は、一端側が第2のバッファ28の出力端と接続され、他端側が伝送ケーブル3の入力端に接続される。第1のインピーダンス素子29は、伝送ケーブル3の信号線34の第1のインピーダンスとの整合を行う抵抗値を有する。例えば、第1のインピーダンス素子29は、抵抗値が50Ωである。

## 【0041】

## 〔伝送ケーブルの構成〕

次に、伝送ケーブル3について説明する。

伝送ケーブル3は、複数の信号線および図示しないライトガイドを用いて構成される。具体的には、伝送ケーブル3は、少なくとも電源電圧VDDを伝送する信号線31と、基準クロック信号を伝送する信号線32と、同期信号を伝送する信号線33と、映像信号を伝送する信号線34と、を有する。なお、実施の形態1では、伝送ケーブル3が伝送路として機能する。また、信号線34は、例えば特性インピーダンスが50Ωに設定される。

20

## 【0042】

## 〔コネクタ部の構成〕

次に、コネクタ部5の構成について説明する。

コネクタ部5は、A/D変換部51と、アナログ・フロント・エンド部52（以下、「AFE部52」という）と、第2のインピーダンス素子53と、を有する。

30

## 【0043】

A/D変換部51は、伝送ケーブル3から伝送された映像信号に対してA/D変換を行ってAFE部52へ出力する。

## 【0044】

AFE部52は、A/D変換部51から入力されたデジタルの映像信号に対してノイズ除去等の所定の信号処理を行ってプロセッサ6へ出力する。AFE部52は、例えばFPGA(Field Programmable Gate Array)等を用いて構成される。

40

## 【0045】

第2のインピーダンス素子53は、一端側が伝送ケーブル3の信号線34の出力端とA/D変換部51との間に接続され他端側がグランドGNDに接続される。第2のインピーダンス素子53は、伝送ケーブル3の信号線34の特性インピーダンスとインピーダンス整合を行う。また、第2のインピーダンス素子53は、例えば抵抗値が50Ωに設定される。

## 【0046】

## 〔プロセッサの構成〕

次に、プロセッサ6の構成について説明する。

プロセッサ6は、電源61と、クロック生成部62と、同期信号生成部63と、画像処理部64と、制御部65と、を備える。

50

## 【0047】

電源61は、外部から入力された電力に基づいて、グランドGNDを基準とした電源電圧VDDを生成し、この生成した電源電圧VDDを伝送ケーブル3の信号線31の中心線を経由させて撮像装置20へ出力するとともに、プロセッサ6を構成する各部へ出力する

。コネクタ部 5 およびプロセッサ 6 側のグランド GND は、信号線 3 1 のシールド線を経由して撮像装置 2 0 側のグランド GND に接続される。

【 0 0 4 8 】

クロック生成部 6 2 は、内視鏡システム 1 の各部の動作の基準となるクロック信号 CLK を生成し、このクロック信号 CLK を伝送ケーブル 3 の信号線 3 3 を経由させて撮像装置 2 0 へ出力する。また、クロック生成部 6 2 は、クロック信号 CLK を同期信号生成部 6 3 および制御部 6 5 の各々へ出力する。クロック生成部 6 2 は、クロック・モジュールを用いて構成される。

【 0 0 4 9 】

同期信号生成部 6 3 は、クロック生成部 6 2 から入力されたクロック信号に基づいて、垂直同期信号、水平同期信号および撮像装置 2 0 を制御するための制御信号を含む同期信号 SYNC を生成し、この同期信号 SYNC を伝送ケーブル 3 の信号線 3 2 を経由して撮像装置 2 0 へ出力する。

【 0 0 5 0 】

画像処理部 6 4 は、コネクタ部 5 の AFE 部 5 2 から入力された映像信号に対して、所定の画像処理を行って表示装置 7 へ出力する。ここで、所定の画像処理としては、例えばホワイトバランス調整処理およびデモザイキング処理等である。画像処理部 6 4 は、GPU (Graphics Processing Unit) 等を用いて構成される。

【 0 0 5 1 】

制御部 6 5 は、内視鏡システム 1 の各部を統括的に制御する。制御部 6 5 は、CPU (Central Processing Unit) 等を用いて構成される。

【 0 0 5 2 】

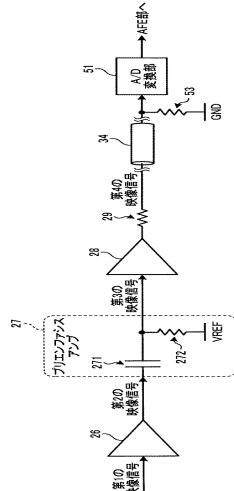

〔 プリエンファシスアンプの構成 〕

次に、上述したプリエンファシスアンプ 2 7 の構成について説明する。図 3 は、プリエンファシスアンプ 2 7 の構成を示す回路図である。

【 0 0 5 3 】

図 3 に示すように、プリエンファシスアンプ 2 7 は、コンデンサ 2 7 1 と、抵抗 2 7 2 と、を有するハイパスフィルタによって構成される。プリエンファシスアンプ 2 7 は、第 1 のバッファ 2 6 から入力された第 2 の映像信号の内、所定の周波数よりも高い周波数成分のみを透過した第 3 の映像信号を第 2 のバッファ 2 8 へ出力する。

【 0 0 5 4 】

コンデンサ 2 7 1 は、一端側が第 1 のバッファ 2 6 の出力端子に接続され、他端側が第 2 のバッファ 2 8 の入力端子に接続される。コンデンサ 2 7 1 は、例えばキャパシタ容量値が 0.8 pF に設定される。

【 0 0 5 5 】

抵抗 2 7 2 は、一端側がコンデンサ 2 7 1 と第 2 のバッファ 2 8 との間に接続され、他端側が外部から入力される基準電圧 VREF が伝送される信号線に接続される。抵抗 2 7 2 は、例えば抵抗値が 10 k に設定される。

【 0 0 5 6 】

このように構成されたプリエンファシスアンプ 2 7 の出力端子における直流インピーダンスは、第 2 のインピーダンス素子 5 3 の直流インピーダンスより高い ( 抵抗 2 7 2 ( 10 k ) ) > 第 2 のインピーダンス素子 5 3 ( ( 50 ) ) 。

【 0 0 5 7 】

〔 撮像装置 2 0 の伝送方法 〕

次に、撮像装置 2 0 が伝送ケーブル 3 を経由してコネクタ部 5 へ映像信号を伝送する伝送方法について説明する。図 4 は、第 4 の映像信号を表すタイミングチャートである。図 4 において、縦軸が電圧を示し、横軸が時間を示す。図 4 において、折れ線 DL が第 4 の映像信号を示す。

【 0 0 5 8 】

図 4 に示すように、映像取得装置の送信部として機能する撮像装置 2 0 は、タイミング

10

20

30

40

50

生成部 25 の制御のもと、第 4 の映像信号を伝送ケーブル 3 の信号線 34 へ出力する。第 4 の映像信号は、所定の値を有する基準レベル信号 VREF\_B と映像レベル信号 D[i] (i は任意の整数) とを周期  $1/f_0$  で交互に出力する。映像レベル信号 D[i] は、受光部 23 を構成するピクセルの受光量に対応した電圧信号であり、ピクセルの受光量がゼロの場合は基準レベル信号 VREF\_B との差分がゼロになる電圧、ピクセルの受光量が飽和レベルに達した場合には基準レベル信号 VREF\_B との差分が Dsat になる電圧を出力する。映像取得装置の受信部として機能する A/D 変換部 51 は、基準レベル信号 VREF\_B の値と映像レベルの値 D[i] との差分 D[i] に対して A/D 変換を行うことによってアナログの第 4 の映像信号をデジタル信号の第 4 の映像信号に変換することによって AFE 部 52 へ出力する。

10

#### 【0059】

〔プリエンファシスアンプの面積について〕

次に、上述したプリエンファシスアンプ 27 と、第 2 のバッファ 28 の出力端と伝送ケーブル 3 の入力端との間に別のプリエンファシスアンプを配置した比較例との効果の違いについて説明する。

#### 【0060】

〔比較例〕

まず、比較例の構成について説明する。図 5 は、比較例のプリエンファシスアンプを備える回路図を模式的に示す図である。図 5 に示す第 2 チップ 1000 に設けられたプリエンファシスアンプ 1001 は、第 2 のバッファ 28 の出力端と伝送ケーブル 3 の信号線 34 の入力端との間に配置される。プリエンファシスアンプ 1001 は、抵抗 29 およびコンデンサ 1002 が直列に配置されることによって、RC ハイパスフィルタを構成する。伝送ケーブル 3 は、上述したように特性インピーダンスが 50 である。このため、所望のハイパスカット周波数を実現するためには、コンデンサ 1002 に大きな容量が必要である。この結果、比較例のプリエンファシスアンプ 1001 は、チップ面積が増大する。

20

#### 【0061】

例えば、比較例のプリエンファシスアンプ 1001 では、50 の抵抗 29 を用いて 20 MHz のハイパスフィルタを実現する場合、以下の式 (1) により、コンデンサ 1002 の容量が 159 pF である。

$$f = 1 / (2 \pi r) = 1 / (2 \pi R C) \quad \dots (1)$$

30

#### 【0062】

1 pF の容量をダブルポリキャパシタで実現する場合 (CMOS OA アンプ回路実務設定の基礎 pp58 を参照)、必要なシリコンの面積は、 $1160 \mu m^2$  である。このため、比較例のプリエンファシスアンプ 1001 では、容量が 159 pF のコンデンサ 1002 をダブルポリキャパシタで実現する場合、 $159 \times 1160 = 429 \mu m \times 429 \mu m$  の面積が必要となる。

#### 【0063】

これに対して、上述したプリエンファシスアンプ 27 のコンデンサ 271 および抵抗 272 によって構成されたハイパスフィルは、インピーダンス整合を考慮する必要がない。このため、抵抗 272 の抵抗値を 10 k およびコンデンサ 271 の容量を 0.8 pF で 20 MHz のハイパスフィルタを実現することができる。ウェル抵抗は、 $3500 / 1 \mu m$  程度の大きさである (CMOS OA アンプ回路実務設定の基礎 pp62 を参照)。このため、10 k の抵抗値を実現する場合、必要なシリコンの面積が  $1 \mu m \times 1.5 \mu m$  程度 (幅 0.5  $\mu m$ 、長さ 1  $\mu m$  の抵抗 3 本で  $10.5 k$  ) となる。また、0.8 pF の容量のコンデンサ 271 を実現する場合、シリコンの面積は、 $0.8 \times 1160 = 31.6 \mu m \times 31 \mu m$  である。

40

#### 【0064】

このように、プリエンファシスアンプ 27 の面積と上述した比較例の面積と比べた場合、圧倒的に小さな面積で実現することができる。

#### 【0065】

50

## 〔プリエンファシスアンプによる効果〕

次に、上述したプリエンファシスアンプ 27 による効果について説明する。図 6 は、プリエンファシスアンプ 27 の効果を模式的に示す図である。図 6 において、図 6 の (a) , (b) , (c) において、横軸が周波数 (Hz) を示し、縦軸がゲイン (dB) を示す。また、図 6 の (a) がケーブルのゲインと周波数特性の関係を示し、図 6 の (b) がプリエンファシスアンプ 27 のハイパスフィルタの特性を示し、図 6 の (c) がプリエンファシスアンプ 27 と細いケーブルの組み合わせ場合のゲインと周波数特性の関係を示す。また、図 6 の (a) の折れ線 L1 が細いケーブルのゲインと周波数特性の関係を示し、折れ線 L2 が太いケーブルのゲインと周波数特性の関係を示す。また、図 6 の (b) の折れ線 L3 がプリエンファシスアンプ 27 のハイパスフィルタの特性を示し、図 6 の (c) の折れ線 L4 がプリエンファシスアンプ 27 と細いケーブルの組み合わせ場合のゲインと周波数特性の関係を示す。

10

## 【0066】

図 6 の (a) の折れ線 L1 および折れ線 L2 に示すように、細いケーブル（例えば上述した信号線 34）は、一次カットオフ周波数が周波数  $f_1$  であり、従来技術で用いた太いケーブルは、一次カットオフ周波数が周波数  $f_2$  ( $f_1 < f_2$ ) である。また、図 6 の (b) の折れ線 L3 に示すように、プリエンファシスアンプ 27 のハイパスフィルタの特性は、一次カットオフ周波数が周波数  $f_3$  となるように設定されている ( $f_1 < f_2 < f_3$ )。

20

## 【0067】

図 6 の (c) の折れ線 L4 に示すように、伝達特性は、細いケーブル（例えば上述した信号線 34）とプリエンファシスアンプ 27 を組み合わせることによって、細いケーブル単体の伝達特性と比べて高い周波数成分の信号伝達を行うことができる。即ち、撮像装置 20 は、第 1 のバッファ 26 と第 2 のバッファ 28 との間にプリエンファシスアンプ 27 を設けることによって、プリエンファシスアンプ 27 のハイパスフィルタの特性によって、DC ゲインが 0 倍となる。しかしながら、撮像装置 20 から送信する映像信号（第 4 の映像信号）は、上述した図 4 のように基準レベル信号 VREF の値と映像信号の値の差分がその振幅を意味する、周波数  $f_0$  のパルス波（交流信号）なので、問題とならない。周波数  $f_1$  と周波数  $f_3$  は、理論上  $f_1 < f_0 < f_3$  となるように設計されることが望ましい。しかしながら、周波数  $f_1$  と周波数  $f_3$  は、設計上の諸制約により、 $f_1 < f_0 < 2 \times f_3$  程度の周波数範囲となるように、設計パラメータが設定されていても構わない。

30

## 【0068】

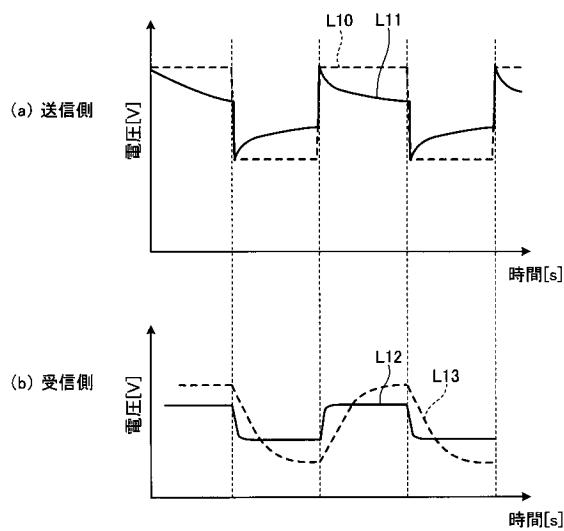

図 7 は、撮像装置 20 が送信する映像信号の時間変化を示す図である。図 7 の (a) , (b) において、横軸が時間 (s) を示し、縦軸が電圧 (V) を示す。また、図 7 において、図 7 の (a) が送信側の映像信号の時間変化を示し、図 7 の (b) が受信側の映像信号の時間変化を示す。図 7 において、曲線 L10 が従来の映像信号の時間変化を示し、曲線 L11 が撮像装置 20 によって出力される映像信号の時間変化を示す。

30

## 【0069】

図 7 の (a) の曲線 L10 に示すように、従来技術では、映像信号をパルス状の信号として送信している。これに対して、図 7 の (a) の曲線 L11 に示すように、撮像装置 20 は、プリエンファシスアンプ 27 によって高周波成分を増幅した状態の映像信号（第 4 の映像信号）を送信する。

40

## 【0070】

図 7 の (b) の曲線 L13 に示すように、従来技術では、伝送ケーブル 3（信号線 34）のローパス特性によって、A/D 変換部 51（受信側）が受信した際の映像信号の高周波成分が減衰するため、映像信号がなまった波形となる。

## 【0071】

これに対して、図 7 の (b) の曲線 L12 に示すように、撮像装置 20 は、プリエンファシスアンプ 27 によって高周波成分を増幅するので、伝送ケーブル 3（信号線 34）のローパス特性によって、A/D 変換部 51（受信側）が受信した際の映像信号が理想的な

50

矩形波状となる。即ち、撮像装置 20 は、第 2 チップ 22 のチップ面積の増大を抑えつつ、細いケーブルであっても、高品質のアナログ信号の映像信号を A/D 変換部 51 へ送信することができる。第 4 の映像信号の周波数  $f_0$  は、 $f_1 < f_0 < f_3$  の条件で最も高い効果が得られるが、少なくとも  $f_1 < f_0$  であれば、本開示の効果を得ることは可能である。

#### 【0072】

以上説明した実施の形態 1 によれば、第 1 のバッファ 26 と第 2 のバッファ 28 との間にプリエンファシスアンプ 27 を配置したので、所望の時定数を有するハイパスフィルタを構成するコンデンサ 271 に対する抵抗 272 の割合を従来よりも大きくできるため、第 1 チップ 21 および第 2 チップ 22 のチップ面積の増大を招くことなく、高速な信号伝送を実現することができる。

10

#### 【0073】

また、実施の形態 1 によれば、撮像装置 20 が伝送ケーブル 3 の信号線 34 の第 1 の特性インピーダンスとの整合を行うための第 1 のインピーダンス素子 29 を有するので、精度よく映像信号をコネクタ部 5 へ送信することができる。

#### 【0074】

また、実施の形態 1 によれば、説明を単純化するために第 2 のバッファ 28 の出力インピーダンスが 0 であり、第 1 のインピーダンス素子 29 の抵抗値が 50 であるものとして説明を行ってきたが、これに限定されることはない。実際の第 2 のバッファ 28 の出力インピーダンスは、数から二十数程度であることが普通であり、その場合には、第 2 のバッファ 28 の出力インピーダンスと第 1 のインピーダンス素子 29 の抵抗値との和が約 50 であることが重要である。即ち、第 1 のインピーダンス素子 29 は、インピーダンス整合という目的のために配置されている限り、必ずしも 50 に限定されることではなく、伝送ケーブル 3 の特性インピーダンス以下の任意の値を取りうる可能性がある。実施の形態 1 において、第 1 のインピーダンス素子 29 は、抵抗器として存在するものとして説明してきたが、第 2 のバッファ 28 の出力端子から伝送ケーブル 3 までのチップ内配線に同等の役割を担わせることも可能であるし、必要に応じて適宜省略することもできる。

20

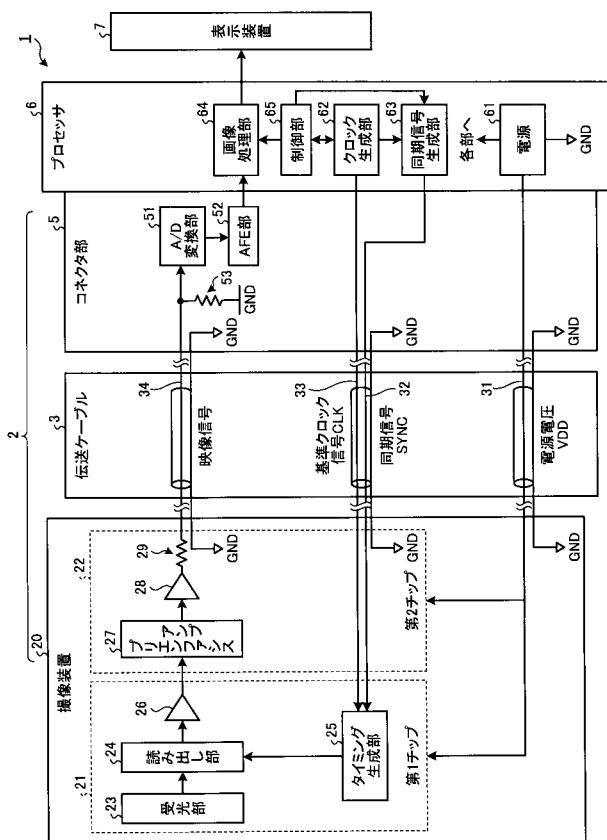

#### 【0075】

##### (実施の形態 2)

次に、本開示の実施の形態 2 について説明する。実施の形態 2 は、上述した実施の形態 1 に係る撮像装置 20 と構成が異なり、第 2 のバッファの閾値ばらつきをキャンセルするバイアス回路と、バイアス回路に電流を供給する定電流源と、さらに備える。以下においては、実施の形態 2 に係る撮像部の構成について説明する。なお、上述した実施の形態 1 に係る撮像装置 20 と同一の構成には同一の符号を付して詳細な説明は省略する。

30

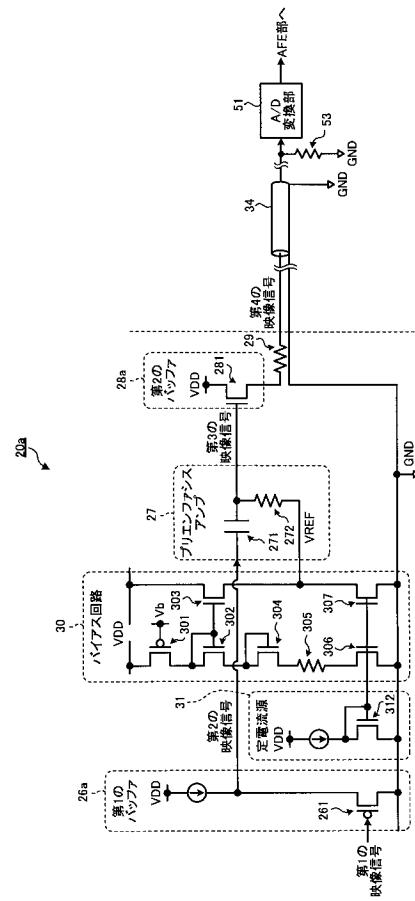

#### 【0076】

##### (撮像装置の構成)

図 8 は、実施の形態 2 に係る撮像装置の要部を含む回路図である。図 8 に示す撮像装置 20a は、第 1 のバッファ 26a と、プリエンファシスアンプ 27 と、第 2 のバッファ 28a と、バイアス回路 30 と、定電流源 31 と、を備える。

40

#### 【0077】

第 1 のバッファ 26a は、上述した図 2 の読み出し部 24 から入力された第 1 の映像信号を低インピーダンスの第 2 の映像信号として増幅することによってプリエンファシスアンプ 27 へ出力する。第 1 のバッファ 26a は、ソースフォロアによって構成される。具体的には、第 1 のバッファ 26a は、PMOS (第 2 導電型) のトランジスタ 261 を有し、ゲート端子に第 1 の映像信号が入力され、ソース端子がプリエンファシスアンプ 27 に接続され、ドレイン端子がグランド GND に接続される。

#### 【0078】

第 2 のバッファ 28a は、プリエンファシスアンプ 27 から入力された第 3 の映像信号の増幅を行った第 4 の映像信号を、第 1 のインピーダンス素子 29 を経由させて伝送ケーブル 3 の信号線 34 へ出力する。第 2 のバッファ 28a は、フィードフォードワード型の

50

アンプを用いて構成される。具体的には、第2のバッファ28aは、NMOSトランジスタ281(第1導電型のトランジスタ)を有する。NMOSトランジスタ281は、ゲート端子にプリエンファシスアンプ27から入力された第3の映像信号が入力され、ソース端子が第1のインピーダンス素子29を経由して伝送ケーブル3の信号線34と接続され、ドレイン端子が電源電圧VDDと接続される。

【0079】

バイアス回路30は、プリエンファシスアンプ27に基準電圧VREFを供給する。具体的には、バイアス回路30は、プリエンファシスアンプ27の直流的な出力電圧である基準電圧VREFを供給する。より具体的には、バイアス回路30は、第2のバッファ28aのNMOSトランジスタ281の閾値のばらつきをキャンセルする基準電圧VREFをプリエンファシスアンプ27へ供給する。バイアス回路30は、カレントミラー回路によって構成される。具体的には、PMOSトランジスタ301と、NMOSトランジスタ302と、NMOSトランジスタ303と、NMOSトランジスタ304と、抵抗305と、NMOSトランジスタ306と、NMOSトランジスタ307と、を有する。

10

【0080】

PMOSトランジスタ301は、ドレイン端子が電源電圧VDDに接続され、ソース端子がNMOSトランジスタ302のソース端子に接続されており、ゲート端子は所定の電圧Vbに接続されている。電圧Vbは、PMOSトランジスタ301を飽和領域で動作させるための電圧であり、例えば図示しないVDD-GND間に形成された抵抗ラダーにより電源電圧を分圧することにより得られる。

20

【0081】

NMOSトランジスタ302は、ゲート端子がNMOSトランジスタ302のドレイン端子およびNMOSトランジスタ303のゲート端子に接続され、ドレイン端子がPMOSトランジスタ301のソース端子およびNMOSトランジスタ302のゲート端子に接続され、ソース端子がNMOSトランジスタ304のゲート端子およびドレイン端子に接続される。

【0082】

NMOSトランジスタ303は、ゲート端子がNMOSトランジスタ302のゲート端子およびドレイン端子に接続され、ドレイン端子が電源電圧VDDに接続され、ソース端子がプリエンファシスアンプ27およびNMOSトランジスタ307のドレイン端子に接続される。

30

【0083】

NMOSトランジスタ304は、ゲート端子がNMOSトランジスタ302のソース端子に接続され、ドレイン端子がNMOSトランジスタ302のソース端子およびNMOSトランジスタ304のゲート端子に接続され、ソース端子が抵抗305に接続される。

【0084】

抵抗305は、一端側がNMOSトランジスタ304のソース端子に接続され、他端側がNMOSトランジスタ306のドレイン端子に接続される。

【0085】

NMOSトランジスタ306は、ゲート端子が定電流源31に接続され、ドレイン端子が抵抗305に接続され、ソース端子がグランドGNDに接続される。

40

【0086】

NMOSトランジスタ307は、ゲート端子が定電流源31に接続され、ドレイン端子がプリエンファシスアンプ27およびNMOSトランジスタ303のソース端子に接続され、ソース端子がグランドGNDに接続される。

【0087】

定電流源31は、バイアス回路30へ電流を供給する。定電流源31は、NMOSトランジスタ312を有する。NMOSトランジスタ312は、ゲート端子がバイアス回路30のNMOSトランジスタ306およびNMOSトランジスタ307のゲート端子およびNMOSトランジスタ312のドレイン端子に接続される。

50

## 【0088】

以上説明した実施の形態2によれば、バイアス回路30がプリエンファシスアンプ27の直流的な出力電圧である基準電圧VREFを供給することによって、第2のバッファ28aのNMOSトランジスタ281の閾値のばらつきをキャンセルする(NMOSトランジスタ281の閾値がプロセスばらつきにより上昇・下降すると、基準電圧VREFもNMOSトランジスタ281の閾値電圧上昇・下降分だけ変動する)ので、上述した実施の形態1と同様の効果を有するとともに、トランジスタの製造ばらつきに対して、消費電力や映像信号のセトリング特性の変動を抑えた映像信号の伝送が可能になる。

## 【0089】

なお、実施の形態2では、バイアス回路30の内部回路構成は、NMOSトランジスタ281の閾値のばらつきをキャンセルする具体的手段の一例を説明しただけであり、NMOSトランジスタ281の閾値がプロセスばらつきによりVだけ変動した際に、基準電圧VREFの電圧がVだけ変動するような回路がバイアス回路30の内部に形成されていれば、本実施例における開示内容に限定されるものではない。

10

## 【0090】

また、実施の形態2では、第1導電型のトランジスタをPMOS、第2導電型のトランジスタをNMOSとして説明してきたが、第2導電型のトランジスタがPMOS、第1導電型のトランジスタがNMOSであり、電源電圧VDDとグランドGNDとを入れ替えた構成であっても、同等の作用および効果が得ることができる。

20

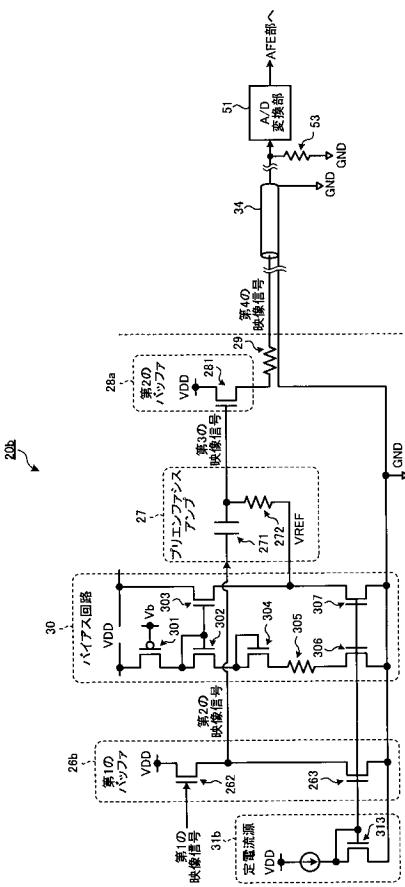

## 【0091】

## (実施の形態2の変形例)

次に、本開示の実施の形態2の変形例について説明する。実施の形態2の変形例は、上述した実施の形態2の撮像装置20aと異なる。以下においては、実施の形態2の変形例に係る撮像装置の構成について説明する。なお、上述した実施の形態2に係る撮像装置20aと同一の構成には同一の符号を付して詳細な説明は省略する。

30

## 【0092】

## 〔撮像装置の構成〕

図9は、実施の形態2の変形例に係る撮像装置の要部を含む回路図である。図9に示す撮像装置20bは、上述した第1のバッファ26aおよび定電流源31に換えて、第1のバッファ26bおよび定電流源31bを備える。

30

## 【0093】

第1のバッファ26bは、上述した図2の読み出し部24から入力された第1の映像信号を低インピーダンスの第2の映像信号として增幅することによってプリエンファシスアンプ27へ出力する。第1のバッファ26bは、ソースフォロアによって構成される。具体的には、第1のバッファ26bは、NMOSトランジスタ262と、NMOSトランジスタ263と、を有する。

40

## 【0094】

NMOSトランジスタ262は、ゲート端子が読み出し部24から入力された第1の映像信号を伝送する信号線に接続され、ドレイン端子が電源電圧VDDに接続され、ソース端子がプリエンファシスアンプ27およびNMOSトランジスタ263のドレイン端子に接続される。

40

## 【0095】

NMOSトランジスタ263は、ゲート端子が定電流源31bから供給される電圧が伝送される信号線が接続され、ドレイン端子がNMOSトランジスタ262のソース端子およびプリエンファシスアンプ27に接続され、ソース端子がグランドGNDに接続される。

50

## 【0096】

定電流源31bは、バイアス回路30および第1のバッファ26bを構成するNMOSトランジスタ263、306、307のゲート端子に電流を供給する。定電流源31bは、NMOSトランジスタ313を有する。NMOSトランジスタ313は、ドレイン端子

50

が電源電圧 V D D に接続され、ソース端子がグランド G N D に接続され、ゲート端子が第 1 のバッファ 2 6 の N M O S トランジスタ 2 6 3 のゲート端子、 N M O S トランジスタ 3 0 6 のゲート端子および N M O S トランジスタ 3 0 7 のゲート端子のそれぞれに接続される。

【 0 0 9 7 】

以上説明した実施の形態 2 の変形例によれば、バイアス回路 3 0 がプリエンファシスアンプ 2 7 の直流的な出力電圧である基準電圧 V R E F を供給することによって、第 2 のバッファ 2 8 a の N M O S トランジスタ 2 8 1 の閾値のばらつきをキャンセルするので、上述した実施の形態 1 と同様の効果を有するとともに、精度よく映像信号を送信することができる。

10

【 0 0 9 8 】

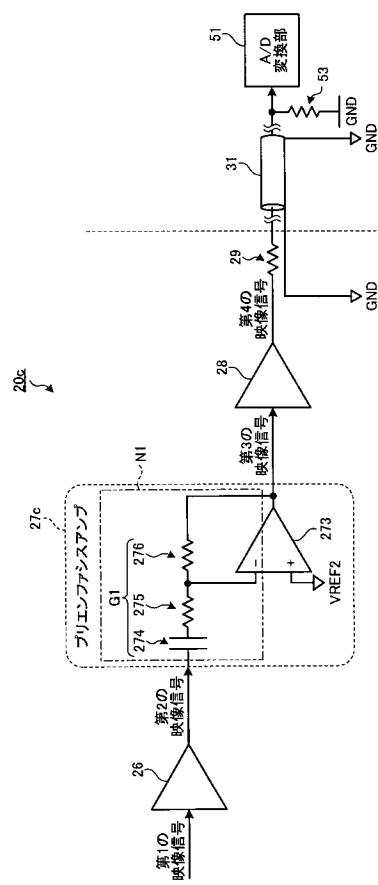

( 実施の形態 3 )

次に、本開示の実施の形態 3 について説明する。実施の形態 3 は、上述した実施の形態 1 に係る撮像装置 2 0 の構成が異なる。以下においては、実施の形態 3 に係る撮像装置の構成について説明する。なお、上述した実施の形態 1 に係る撮像装置 2 0 と同一の構成には同一の符号を付して詳細な説明は省略する。

【 0 0 9 9 】

[ 撮像装置の構成 ]

図 1 0 は、実施の形態 3 に係る撮像装置の要部を含む回路図である。図 1 0 に示す撮像装置 2 0 c は、上述した実施の形態 1 に係るプリエンファシスアンプ 2 7 に換えて、プリエンファシスアンプ 2 7 c を備える。

20

【 0 1 0 0 】

プリエンファシスアンプ 2 7 c は、第 1 のバッファ 2 6 から入力された第 2 の映像信号の内、所定の周波数よりも高い周波数成分のみを透過しつつ増幅を行った第 3 の映像信号を第 2 のバッファ 2 8 へ出力する。プリエンファシスアンプ 2 7 c は、フィードバックネットワーク N 1 を有するフィードバックアンプ 2 7 3 と、フィードバックネットワーク N 1 内に設けられ、フィードバックアンプ 2 7 3 の周波数依存性を有する第 3 のインピーダンス素子群 G 1 と、を含む。

【 0 1 0 1 】

第 3 のインピーダンス素子群 G 1 は、コンデンサ 2 7 4 ( C i n ) と、抵抗 2 7 5 ( R i n ) と、抵抗 2 7 6 ( R f ) と、を有する。コンデンサ 2 7 4 は、一端側が第 1 のバッファ 2 6 の出力端 ( 第 3 のインピーダンス素子群 G 1 の第 1 入力端子 ) に接続され、他端側が抵抗 2 7 5 に接続される。抵抗 2 7 5 は、一端側がコンデンサ 2 7 4 に接続され、他端側が抵抗 2 7 5 とフィードバックアンプ 2 7 3 の入力端子 ( - 端子 ) に接続される。抵抗 2 7 6 は、一端側が抵抗 2 7 5 および入力端子 ( - 端子 ) に接続され、他端側がフィードバックアンプ 2 7 3 の出力端子に接続される。

30

【 0 1 0 2 】

フィードバックアンプ 2 7 3 は、入力端子 ( - 端子 ) が第 3 のインピーダンス素子群 G 1 の第 2 入力端子に接続され、入力端子 ( + 端子 ) が第 2 の基準電圧 V R E F 2 に接続され、出力端子が第 2 のバッファ 2 8 の入力端子および第 3 のインピーダンス素子群 G 1 の第 3 入力端子に接続される。

40

【 0 1 0 3 】

このように構成されたプリエンファシスアンプ 2 7 c は、以下の式 ( 2 ) を満たす。

【 数 1 】

$$\frac{V_{OUT}}{V_{IN}} = -\frac{R_f}{R_{in}} \frac{sC_{in}R_{in}}{1+sC_{in}R_{in}} \quad \dots (2)$$

【 0 1 0 4 】

以上説明した実施の形態 3 によれば、プリエンファシスアンプ 2 7 c が第 1 のバッファ 2 6 から入力された第 2 の映像信号の内、所定の周波数よりも高い周波数成分のみを透過

50

しつつ増幅を行った第3の映像信号を第2のバッファ28へ出力するので、伝送ケーブル3の細径化と高速な信号伝送との両立を図ることができる。

【0105】

(その他の実施の形態)

上述した本開示の実施の形態1～3に開示されている複数の構成要素を適宜組み合わせることによって、種々の発明を形成することができる。例えば、上述した本開示の実施の形態1～3に記載した全構成要素からいくつかの構成要素を削除してもよい。さらに、上述した本開示の実施の形態1～3で説明した構成要素を適宜組み合わせてもよい。

【0106】

また、本開示の実施の形態1～3では、制御装置と光源装置とが別体であったが、一体的に形成してもよい。

10

【0107】

また、本開示の実施の形態1～3では、内視鏡システムであったが、例えば被検体を撮像するビデオマイクロスコープ、撮像機能を有する携帯電話および撮像機能を有するタブレット型端末であっても適用することができる。

【0108】

また、本開示の実施の形態1～3では、軟性の内視鏡を備えた内視鏡システムであったが、硬性の内視鏡を備えた内視鏡システム、工業用の内視鏡を備えた内視鏡システムであっても適用することができる。

20

【0109】

また、本開示の実施の形態1～3では、被検体に挿入される内視鏡を備えた内視鏡システムであったが、例えば硬性の内視鏡を備えた内視鏡システム、副鼻腔内視鏡および電気メスや検査プローブ等の内視鏡システムであっても適用することができる。

【0110】

また、本開示の実施の形態1～3では、上述してきた「部」は、「手段」や「回路」などに読み替えることができる。例えば、制御部は、制御手段や制御回路に読み替えることができる。

【0111】

以上、本願の実施の形態のいくつかを図面に基づいて詳細に説明したが、これらは例示であり、本発明の開示の欄に記載の態様を始めとして、当業者の知識に基づいて種々の変形、改良を施した他の形態で本発明を実施することが可能である。

30

【符号の説明】

【0112】

1 内視鏡システム

40

2 内視鏡

3 伝送ケーブル

4 操作部

5 コネクタ部

6 プロセッサ

7 表示装置

8 光源装置

20, 20a, 20b, 20c 撮像装置

21 第1チップ

22 第2チップ

23 受光部

24 読み出し部

25 タイミング生成部

26, 26a, 26b 第1のバッファ

27, 27c プリエンファシスアンプ

27c プリエンファシスアンプ

50

28, 28a 第2のバッファ

29 第1のインピーダンス素子

30 バイアス回路

31, 31b 定電流源

51 A/D変換部

52 AFE部

53 第2のインピーダンス素子

61 電源

62 クロック生成部

63 同期信号生成部

64 画像処理部

65 制御部

100 挿入部

101 先端部

102 基端部

273 フィードバックアンプ

G1 第3のインピーダンス素子群

10

【図1】

【図2】

【 四 3 】

## 【 図 5 】

【 図 4 】

【 図 6 】

【 义 7 】

【 図 8 】

〔 図 9 〕

【 図 1 0 】

---

フロントページの続き

|                |         |            |

|----------------|---------|------------|

| (51) Int.Cl.   | F I     | テーマコード(参考) |

| <b>A 6 1 B</b> | 1/00    | (2006.01)  |

|                | H 0 4 N | 7/18       |

|                | A 6 1 B | 1/00       |

|                |         | 6 8 0      |

|                |                                                                                                                                                                                                                                                              |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 视频采集装置和内窥镜                                                                                                                                                                                                                                                   |         |            |

| 公开(公告)号        | <a href="#">JP2019213120A</a>                                                                                                                                                                                                                                | 公开(公告)日 | 2019-12-12 |

| 申请号            | JP2018109615                                                                                                                                                                                                                                                 | 申请日     | 2018-06-07 |

| [标]申请(专利权)人(译) | 奥林巴斯株式会社                                                                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 奥林巴斯公司                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | 大澤雅人                                                                                                                                                                                                                                                         |         |            |

| 发明人            | 大澤 雅人                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | H04N7/18 A61B1/045 H04N5/225 H04N5/232 G02B23/24 A61B1/00                                                                                                                                                                                                    |         |            |

| FI分类号          | H04N7/18.M A61B1/045.610 H04N5/225.500 H04N5/232.300 G02B23/24.B H04N7/18.A A61B1/00.680                                                                                                                                                                     |         |            |

| F-TERM分类号      | 2H040/DA22 2H040/GA02 2H040/GA06 2H040/GA11 4C161/CC06 4C161/NN01 4C161/NN03 4C161/SS07 4C161/SS12 4C161/UU02 4C161/UU09 5C054/CA04 5C054/CC02 5C054/ED12 5C054/HA12 5C122/DA26 5C122/EA54 5C122/GC52 5C122/GC86 5C122/HA34 5C122/HB02 5C122/HB07 5C122/HB10 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                    |         |            |

## 摘要(译)

为了提供可以同时减小传输电缆直径和高速信号传输的视频采集设备和内窥镜。解决方案：一种视频采集设备包括第一缓冲器26，输出第三视频的预加重放大器27。在从第一缓冲器26输入的第二视频信号中仅传输高于预定频率的频率分量的同时放大的信号，以及输出通过放大从前置放大器输入的第三视频信号而获得的第四视频信号的第二缓冲器28 增强放大器27连接到传输电缆3的输入端，并且预增强放大器27输出端的DC阻抗高于第一阻抗元件53的DC阻抗。图3